USB總線接口芯片CH371及其在集成電路設計中的應用

隨著計算機外設的日益豐富和即插即用需求的增長,通用串行總線(USB)因其高速、穩定和易用性,已成為主流的設備連接標準。在實現非USB設備與計算機通信的過程中,專用的USB接口芯片扮演著關鍵角色。其中,沁恒微電子(WCH)推出的CH371芯片,以其高集成度和簡便易用的特點,在嵌入式系統和集成電路輔助設計中得到了廣泛應用。

一、CH371芯片概述

CH371是一款用于計算機擴展USB總線的通用接口芯片。它內部集成了USB通信協議處理單元、數據緩沖區、控制邏輯以及通用的并行或串行接口,從而將復雜的USB協議轉換為簡單的本地總線操作。其主要特點包括:

- 協議透明化:芯片自動處理底層的USB通信協議(如令牌包、數據包、握手包),開發者無需深入理解USB協議細節,大大降低了開發門檻。

- 接口靈活:提供并行接口(類似單片機總線)和異步串行接口,可方便地與微控制器(MCU)、數字信號處理器(DSP)或可編程邏輯器件(FPGA/CPLD)連接。

- 即插即用:支持USB 1.1規范,具備全速(12Mbps)傳輸能力,并兼容USB供電模式。

- 內置固件:芯片在出廠時已固化標準驅動程序,在Windows等操作系統下可自動識別為通用設備,簡化了主機端驅動開發。

二、CH371在集成電路設計中的應用價值

在集成電路(IC)設計,特別是數字IC和系統級芯片(SoC)的設計驗證階段,CH371能發揮重要作用,主要體現在以下幾個方面:

1. 原型驗證與數據交換

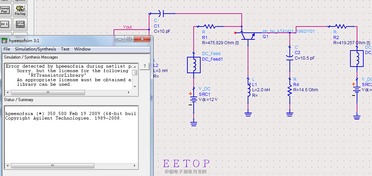

在芯片流片(Tape-out)之前,設計通常需要在FPGA平臺上進行原型驗證。CH371可以為FPGA原型驗證板提供一條高速、穩定的PC連接通道。通過它,設計工程師可以:

- 快速下載配置數據:將設計生成的比特流文件通過USB口快速下載到FPGA中。

- 實時調試與監控:在PC端的上位機軟件控制下,通過USB總線向FPGA內的設計模塊發送測試向量(Test Vectors),并實時讀回內部寄存器狀態、信號波形或處理結果,極大提高了調試效率。

- 大數據量傳輸:對于涉及圖像處理、信號處理等需要處理大量數據的芯片設計,CH371可以作為FPGA與PC間的高速數據管道,用于上傳原始數據或下載處理結果。

2. 構建簡易的專用測試設備(ATE)接口

在芯片初樣測試階段,可能需要構建臨時的自動化測試平臺。利用CH371,可以快速搭建一個基于PC的測試系統:

- 控制核心:PC作為主控制器,運行測試程序。

- 接口橋梁:CH371芯片負責USB通信,其并口連接到一個自定義的測試板,板上包含待測芯片(DUT)的插座、電源管理、時鐘電路及必要的電平轉換。

- 執行測試:PC通過CH371發送測試命令和激勵信號,并采集待測芯片的輸出響應,實現自動化功能測試與參數測量。

3. 輔助設計工具與知識產權(IP)核驗證

一些EDA工具或自主開發的IP核(如通信編解碼器、加密算法模塊)需要在實際數據傳輸環境中驗證其性能。設計者可以利用CH371搭建一個“硬件在環”測試平臺:

- 將IP核實現到FPGA中。

- 使用CH371在FPGA與運行仿真軟件的PC之間建立物理連接。

- PC軟件生成仿真數據流,通過USB發送給FPGA中的IP核處理,再將結果回傳比對,從而在接近真實的環境中驗證IP核的正確性和穩健性。

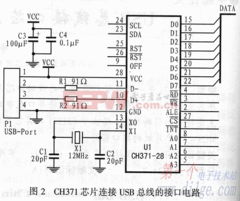

三、典型應用電路設計要點

在設計基于CH371的應用電路時,需關注以下幾點:

- 接口模式選擇:根據主控端(如MCU)的接口資源,選擇并行或串行模式。并行模式速度快,控制簡單;串行模式節省I/O引腳。

- 電源與時鐘:CH371通常從USB總線取電(5V),需注意內部3.3V LDO的輸出能力是否能滿足外圍電路需求。其時鐘可由外部晶振提供,也可使用內置振蕩器。

- 信號完整性:USB差分數據線(D+, D-)的走線應等長、緊密耦合,并做好阻抗匹配,以保證通信穩定性。

- 外圍電路簡化:CH371集成度高,外圍通常僅需少量電阻、電容和晶振即可工作,這有利于減少電路板面積,降低整體設計復雜度。

###

CH371作為一款成熟的USB接口芯片,通過將復雜的USB協議標準化、硬件化,為嵌入式系統與計算機的互聯提供了一條便捷的橋梁。在集成電路設計領域,它不僅是功能驗證和原型調試的得力助手,也為快速構建低成本專用測試系統提供了可能。其易于集成、開發周期短的特點,使其成為工程師在實現設備USB化、進行數據采集與交互控制時的經典選擇之一,充分體現了專用接口芯片在系統設計中的價值。

如若轉載,請注明出處:http://www.fuiun.cn/product/7.html

更新時間:2026-03-07 16:16:42